# 600kHz 3A Step-Down Switching Regulator

### **FEATURES**

- Integrated 3 Amp switch

- 600kHz frequency of operation

- Current mode controller

- Precision enable threshold

- Available in SOP8-PP Package

## APPLICATION

- XDSL Modems

- CPE equipment

- DC-DC point of load applications

- Portable equipment

#### ORDERING INFORMATION

| Device (Marking) | Package |  |  |

|------------------|---------|--|--|

| TJ4519DP         | SOP8-PP |  |  |

## DESCRIPSION

The TJ4519 is a current mode switching regulator with an integrated switch, operating at 600kHz with enable functions. The integrated switch allows for cost effective low power solutions (peak switch current 3 amps). High frequency of operation allows for very small passive components. Current mode operation allows for fast dynamic response and instantaneous duty cycle adjustment as the input varies (ideal for CPE applications where the input is a wall plug power). The low shutdown current makes it ideal for portable applications where battery life is important.

## **Absolute Maximum Ratings**

| CHARACTERISTIC                       | SYMBOL                             | MIN. | MAX. | UNIT |

|--------------------------------------|------------------------------------|------|------|------|

| Input Supply Voltage                 | V <sub>IN</sub>                    | -0.3 | 28   | V    |

| Boost Pin Above VSW                  | V <sub>BST</sub> - V <sub>SW</sub> | -    | 16   | V    |

| Boost Pin Voltage                    | V <sub>BST</sub>                   | -0.3 | 32   | V    |

| EN Pin Voltage                       | V <sub>EN</sub>                    | -0.3 | 24   | V    |

| FB Pin Voltage                       | V <sub>FB</sub>                    | -0.3 | 6    | V    |

| FB Pin Current                       | I <sub>FB</sub>                    | -    | 1    | mA   |

| Operating Ambient Temperature Range  | T <sub>A</sub>                     | -40  | 85   | °C   |

| Operating Junction Temperature Range | TJ                                 | -40  | 150  | °C   |

| Storage Temperature Range            | T <sub>STG</sub>                   | -65  | 150  | °C   |

| Lead Temperature (Soldering) 5 sec   | T <sub>SOL</sub>                   | -    | 260  | °C   |

(1) For proper operation of device, V<sub>IN</sub> should be within Max. Operating Input Voltage as defined in Electrical Characteristics.

## **Ordering Information**

| Order No.   | Package | Description                   | Package Marking | Supplied As |

|-------------|---------|-------------------------------|-----------------|-------------|

| TJ4519DP-8L | SOP8-PP | 600kHz 3A Step-Down Regulator | TJ4519          | Reel        |

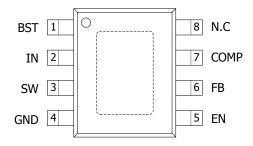

## **PIN CONFIGURATION**

SOP8-PP (With Exposed PAD)

## **PIN DESCRIPTION**

| Pin No. | Pin Name            | Pin Description                                                                                                                                                                                                              |  |  |

|---------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | BST                 | Provides power to the internal NPN switch. The minimum turn on voltage for this switch is 2.7V.                                                                                                                              |  |  |

| 2       | IN                  | Pin IN delivers all power required by control and power circuitry. This pin sees high di/dt during switching. A decoupling capacitor should be attached to this pin as close as possible.                                    |  |  |

| 3       | SW                  | Pin SW is the emitter of the internal switch. The external freewheelin diode should be connected as close as possible to this pin.                                                                                           |  |  |

| 4       | GND                 | Ground. All voltages are measured with respect to this pin. The decoupling capacitor and the freewheeling diode should be connected to GND as short as possible.                                                             |  |  |

| 5       | EN                  | This is the chip enable input. The regulator is switched on if EN is high,<br>and it is off if EN is low. The regulator is in standby mode when EN is<br>low, and the input supply current is reduced to a few microamperes. |  |  |

| 6       | FB                  | Feedback input for adjustable output controllers.                                                                                                                                                                            |  |  |

| 7       | COMP                | The output of the internal error amplifier and input of the peak current comparator. A compensation network is connected to this pin to achieve the specified performance.                                                   |  |  |

| 8       | N.C                 | Not Connect.                                                                                                                                                                                                                 |  |  |

| -       | Exposed Thermal PAD | Pad for heat sinking purposes. Connect to ground plane using multiple vias. Not connected internally.                                                                                                                        |  |  |

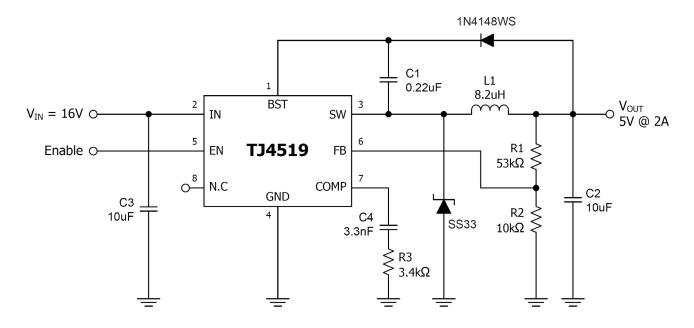

## **TYPICAL APPLICATION**

\* See Application Information.

## **ELECTRICAL CHARACTERISTICS**

Unless specified:  $V_{IN}$  = 12V,  $V_{COMP}$  = 0.8V,  $V_{BST}$  =  $V_{IN}$  + 5V, EN = tied to  $V_{IN}$ , SW = open.  $T_J$  = -40°C to 125°C.

| PARAMETER                                                   | SYMBOL              | TEST CONDITION                                    | MIN.  | TYP.  | MAX.              | UNIT |

|-------------------------------------------------------------|---------------------|---------------------------------------------------|-------|-------|-------------------|------|

| Operating Input Voltage                                     | V <sub>IN</sub>     |                                                   |       |       | 24 <sup>(1)</sup> | V    |

| Maximum Switch Current Limit                                | I <sub>SW</sub>     | T <sub>A</sub> = 25℃, D = 50%                     | 3.5   |       | 5.5               | А    |

| Oscillator Frequency                                        | fosc                |                                                   | 500   | 600   | 700               | kHz  |

| Switch On Voltage Drop                                      | V <sub>D(SW)</sub>  | I <sub>SW</sub> = 3A                              |       | 570   |                   | mV   |

| V <sub>IN</sub> Undervoltage Lockout                        | V <sub>UVLO</sub>   |                                                   |       | 3.9   | 4.4               | V    |

| VIN UVLO Hysteresis                                         |                     |                                                   |       | 60    |                   | mV   |

| V <sub>IN</sub> Supply Current                              | ΙQ                  | V <sub>FB</sub> = 1V                              |       | 3     | 5                 | mA   |

| FB Input Current                                            | I <sub>Q(OFF)</sub> | V <sub>EN</sub> = 0V                              |       | -0.25 | -1                | uA   |

| Feedback Voltage                                            | V <sub>FB</sub>     |                                                   | 0.784 | 0.8   | 0.816             | V    |

| Feedback Voltage Line Regulation                            |                     | $4.4V < V_{IN} < 24V^{(2)}$                       |       | +3    |                   | mV/V |

| FB to $V_{COMP}$ Voltage Gain <sup>(3)</sup>                |                     | $0.9V \le V_{COMP} \le 2.0V$                      | 150   | 350   |                   | V/V  |

| FB to V <sub>COMP</sub> Transconductance <sup>(3)</sup>     |                     | $\Delta I_{COMP} = \pm 10 \mu A$                  | 500   | 850   | 1300              | uMho |

| V <sub>COMP</sub> Pin Source Current                        |                     | V <sub>FB</sub> = 0.6V                            |       | 70    | 110               | uA   |

| V <sub>COMP</sub> Pin Sink Current                          |                     | V <sub>FB</sub> = 1.0V                            |       | -70   | -110              | uA   |

| V <sub>COMP</sub> Pin to Switch Current<br>Transconductance |                     | V <sub>COMP</sub> = 1.25V                         |       | 5     |                   | A/V  |

| V <sub>COMP</sub> Pin<br>Maximum Switching Threshold        |                     | Duty cycle = 0%                                   |       | 0.6   |                   | V    |

| V <sub>COMP</sub> OCP Threshold                             |                     | V <sub>COMP</sub> rising                          |       | 2     |                   | V    |

| V <sub>COMP</sub> Hiccup Retry Threshold                    |                     | V <sub>COMP</sub> falling                         |       | 0.25  |                   | V    |

| Maximum, Switch Duty Cycle                                  |                     | V <sub>COMP</sub> = 1.2V, I <sub>SW</sub> = 400mA | 85    |       |                   | %    |

| Minimum Boost Voltage<br>Above Switch                       |                     |                                                   |       | 2.7   |                   | V    |

|                                                             |                     | I <sub>SW</sub> = 1A                              |       | 10    | 15                | - mA |

| Boost Current                                               |                     | I <sub>SW</sub> = 3A                              |       | 30    | 45                |      |

| Enable Input Threshold Voltage                              | V <sub>ETH</sub>    |                                                   | 1.1   | 1.27  | 1.5               | V    |

| Frankla Outrast Dia 20 and 1                                | I <sub>EOL</sub>    | EN = 50mV below threshold                         |       | 8     |                   | uA   |

| Enable Output Bias Current                                  | I <sub>EOH</sub>    | EN = 50mV above threshold                         |       | 10    |                   | uA   |

(1) The device may not function properly outside its operating input voltage range.(2) The required minimum input voltage for a regulated output depends on the output voltage and load condition.

(3) Guaranteed by design.

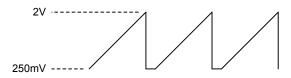

### **APPLICATION INFORMATION**

The TJ4519 is a current mode buck converter regulator. TJ4519 has an internal fixed-frequency clock. The TJ4519 uses two feedback loops that control the duty cycle of the internal power switch. The error amplifier functions like that of the voltage mode converter. The output of the error amplifier works as a switch current reference. This technique effectively removes one of the double poles in the voltage mode system. With this, it is much simpler to compensate a current mode converter to have better performance. The current sense amplifier in the TJ4519 monitors the switch current during each cycle. Overcurrent protection (OCP) is triggered when the current limit exceeds the upper limit of 3A, detected by a voltage on COMP greater than about 2V. When an OCP fault is detected, the switch is turned off and the external COMP capacitor is quickly discharged using an internal npn transistor. Once the COMP voltage has fallen below 250mV, an internal timer prevents any operation for 50µs, after which the part enters a normal startup cycle. In the case of sustained overcurrent or dead-short, the part will continually cycle through the retry sequence as described above, at a rate dependent on the value of Ccomp. During start up, the voltage on COMP. Therefore, the retry time for a sustained overcurrent can be approximately calculated as:

$$T_{retry} = C_{comp} \cdot \frac{2V}{120uA} + 50us$$

Figure 1 shows the voltage on COMP during a sustained overcurrent condition.

Figure 1. Voltage on COMP for Startup and OCP

#### Enable

Pulling and holding the EN pin below 0.4V activates the shut down mode of the TJ4519 which reduces the input supply current to less than 10uA. During the shut down mode, the switch is turned off. The TJ4519 is turned on if the EN pin is pulled high.

#### Oscillator

Its internal free running oscillator sets the PWM frequency at 600 kHz for the TJ4519 without any external components to program the frequency.

#### UVLO

When the EN pin is pulled and held above 1.8Vm, the voltage on Pin IN determines the operation of the TJ4519. As VIN increases during power up, the internal circuit senses VIN and keeps the power transistor off until VIN reaches 2.6V

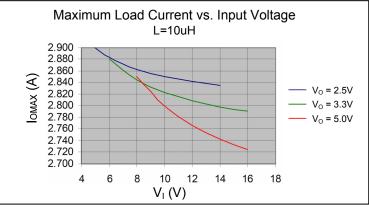

#### Load current

The peak current  $I_{PEAK}$  in the switch is internally limited. For a specific application, the allowed load current ICMAX will change if the input voltage drifts away from the original design as given for continuous current mode:

$$I_{OMAX} = 3 - \frac{V_O \cdot (1-D)}{2 \cdot L \cdot f_s}$$

Where:

$f_{S}$  = switching frequency,  $V_{O}$  = output voltage D = duty ratio,  $V_{O}/V_{I}$  $V_{I}$  = input Voltage.

Figure 2 shows the theoretical maximum load current for the specific cases. In a real application, however, the allowed maximum load current also depends on the layout and the air cooling condition. Therefore, the maximum load current may need to be degraded according to the thermal situation of the application.

Figure 2. Theoretical maximum load current curves

#### Inductor Selection

The factors for selecting the inductor include its cost, efficiency, size and EMI. For a typical TJ4519 application, the inductor selection is mainly based on its value, saturation current and DC resistance. Increasing the inductor value will decrease the ripple level of the output voltage while the output transient response will be degraded. Low value inductors offer small size and fast transient responses while they allow large ripple currents, poor efficiencies and require more output capacitance for low output ripple. The inductor should be able to handle the peak current without saturating and its copper resistance in the winding should be as low as possible to minimize its resistive power loss. A good trade-off among its size, loss and cost is to set the inductor ripple current to be within 15% to 30% of the maximum output current.

The inductor value can be determined according to its operating point under its continuous mode and the switching frequency as follows:

$$L = \frac{V_{O} \cdot (V_{I} - V_{O})}{V_{I} \cdot f_{s} \cdot \delta \cdot I_{OMAX}}$$

Where : fs = switching frequency,

$\delta$  = ratio of the peak to peak inductor current to the output load current Vo = output voltage.

The peak to peak inductor current is:

$$I_{p-p} = \delta \cdot I_{OMAX}$$

After the required inductor value is selected, the proper selection of the core material is based on the peak inductor of the core material is based on the peak inductor current and efficiency specifications. The core must be able to handle the peak inductor current  $I_{PEAK}$  without saturation and produce low core loss during the high frequency operation.

$$I_{\text{PEAK}} = I_{\text{OMAX}} + \frac{I_{p-p}}{2}$$

The power loss for the inductor includes its core loss and copper loss. If possible, the winding resistance should be minimized to reduce inductor's copper loss. The core must be able to handle the peak inductor current  $I_{PEAK}$  without saturation and produce low core loss during the high frequency operation. The core can be found in the manufacturer's datasheet. The inductor's copper loss can be estimated as follows:

$$\mathsf{P}_{\mathsf{COPPER}} = \mathsf{I}^2_{\mathsf{LRMS}} \cdot \mathsf{R}_{\mathsf{WINDING}}$$

Where:

$I_{\mbox{\scriptsize LRMS}}$  is the RMS current in the inductor. This current can be calculated as follows:

$$I_{LRMS} = I_{OMAX} \cdot \sqrt{1 + \frac{1}{12} \cdot \delta^2}$$

#### **Output Capacitor Selection**

Basically, there are two major factors to consider in selecting the type and quantity of the output capacitors. The first one is the required ESR (Equivalent Series Resistance) which should be low enough to reduce the output voltage deviation during load changes. The second one is the required capacitance, which should be high enough to hold up the output voltage. Before the TJ4519 regulates the inductor current to a new value during a load transient, the output capacitor delivers all the additional current needed by the load. The ESR and ESL of the output capacitor, the loop parasitic inductance between the output capacitor and the load combined with inductor ripple current are all major contributors to the output voltage ripple. Surface mount ceramic capacitors are recommended.

#### Input Capacitor Selection

The input capacitor selection is based on its ripple current level, required capacitance and voltage rating. This capacitor must be able to provide the ripple current drawn by the converter. For the continuous conduction mode, the RMS value of the input capacitor current  $I_{CIN(RMS)}$  can be calculated from:

$$I_{\text{CIN(RMS)}} = I_{\text{OMAX}} \cdot \sqrt{\frac{V_{\text{O}} \cdot (V_{\text{I}} - V_{\text{O}})}{V_{\text{I}}^2}}$$

This current gives the capacitor's power loss through its  $R_{CIN(ESR)}$  as follows:

$$P_{CIN} = I_{CIN(RMS)}^2 \bullet R_{CIN(ESR)}$$

The input ripple voltage mainly depends on the input capacitor's ESR and its capacitance for a given load, input voltage and output voltage. Assuming that the input current of the converter is constant, the required input capacitances for a given voltage ripple can be calculated by:

$C_{\text{IN}} = I_{\text{OMAX}} \bullet \frac{D \bullet (1 \text{-} D)}{f_{\text{s}} \bullet (\Delta V_{\text{I}} \quad I_{\text{OMAX}} \bullet R_{\text{CIN(ESR)}})}$

Where:  $\Delta V_{I}$  = the given input voltage ripple.

Because the input capacitor is exposed to the large surge current, attention is needed for the input capacitor. If tantalum capacitors are used at the input side of the converter, one needs to ensure that the RMS and surge ratings are not exceeded. For generic tantalum capacitors, it is suggested to derate their voltage ratings at a ratio of about two to protect these input capacitors.

#### **Boost Capacitor and its Supply Source Selection**

The boost capacitor selection is based on its discharge ripple voltage, worst case conduction time and boost current. The worst case conduction time and boost current. The worst case conduction time  $T_w$  can be estimated as follows:

$$T_W = \frac{1}{f_s} \cdot D_{max}$$

Where:  $f_{S}$  = the switching frequency,  $D_{max}$  = maximum duty ratio, 0.85 for the TJ4915.

The required minimum capacitance for the boost capacitor will be:

$$C_{\text{boost}} = \frac{I_{\text{B}}}{V_{\text{D}}} \cdot T_{\text{W}}$$

Where:  $I_B$  = the boost current and  $V_D$ = discharge ripple voltage.

With  $f_S = 600$ kHz,  $V_D = 0.5$ V and  $I_B = 0.045$ A, the required minimum capacitance for the boost capacitor is:

$$C_{\text{boost}} = \frac{I_B}{V_D} \cdot \frac{1}{f_s} \cdot D_{\text{max}} = \frac{0.045}{0.5} \cdot \frac{1}{600k} \cdot 0.85 = 128$$

nF

The internal driver of the switch requires a minimum 2.7V to fully turn on that switch to reduce its conduction loss. If the output voltage is less than 2.7V, the boost capacitor can be connected to either the input side or an independent supply with a decoupling capacitor. But the Pin BST should not see a voltage higher than its maximum rating.

#### **Freewheeling Diode Selection**

This diode conducts during the switch's off-time. The diode should have enough current capability for full load and short circuit conditions without any thermal concerns. Its maximum repetitive reverse block voltage has to be higher than the input voltage of the TJ4519. A low forward conduction drop is also required to increase the overall efficiency. The freewheeling diode should be turned on and off fast with minimum reverse recovery because the TJ4519 is designed for high frequency applications. SS23 Schottky rectifier is recommended for certain applications. The average current of the diode, I<sub>D-AVG</sub> can be calculated by:

$\mathsf{I}_{\mathsf{D}-\mathsf{AVG}} = \mathsf{I}_{\mathsf{OMAX}} \bullet (\mathsf{I} - \mathsf{D})$

#### **Thermal Considerations**

There are three major power dissipation sources for the TJ4519. The internal switch conduction loss its switching loss due to the high frequency switching actions and the base drive boost circuit loss. These losses can be estimated as:

$$P_{\text{total}} = I_0^2 \cdot R_{\text{on}} \cdot D + 10.8 \cdot 10^{-3} \cdot I_0 \cdot V_1 + \frac{10}{1000} \cdot I_0 \cdot D \cdot (V_{\text{boost}})$$

Where:  $I_0$  = load current; Ron = on-equivalent resistance of the switch;  $V_{BOOST}$  = input voltage or output based on the boost circuit connection.

The junction temperature of the TJ4519 can be further determined by:

$$T_{J} = T_{A} + \theta_{JA} \cdot P_{total}$$

$\theta_{JA}$  is the thermal resistance from junction to ambient. Its value is a function of the IC package, the application layout and the air cooling system.

The freewheeling diode also contributes a significant portion of the total converter loss. This loss should be minimized to increase the converter efficiency by using Schottky diodes with low forward drop ( $V_F$ ).

$$\mathsf{P}_{\mathsf{diode}} = \mathsf{V}_{\mathsf{F}} \bullet \mathsf{I}_{\mathsf{O}} \bullet (1 - \mathsf{D})$$

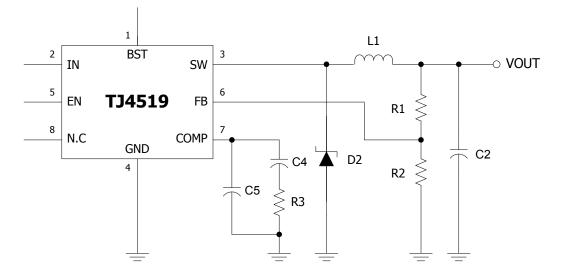

#### Loop Compensation Design

The TJ4519 has an internal error amplifier and requires a compensation network to connect between the COMP pin and GND pin as shown in Figure 3. The compensation network includes C4, C5 and R3. R1 and R2 are used to program the output voltage according to:

$$V_0 = 0.8 \cdot (1 + \frac{R_1}{R_2})$$

Assuming the power stage ESR (equivalent series resistance) zero is an order of magnitude higher than the closed loop bandwidth, which is typically one tenth of the switching frequency, the power stage control to output transfer function with the current loop closed (Ridley model) for the TJ4519 will be as follows:

$$G_{VD}(s) = \frac{2.5 \cdot R_L}{1 + \frac{s}{\frac{1}{R_L \cdot C}}}$$

Where:  $R_L = Load$ , C = Output capacitor.

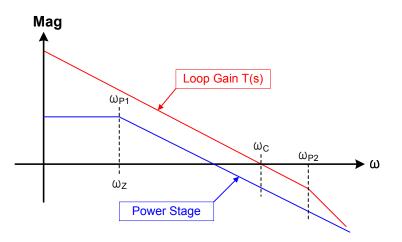

The goal of the compensation design is to shape the loop to have a high DC gain, high bandwidth, enough phase margin, and high attenuation for high frequency noises. Figure 3 gives a typical compensation network which offers 2 poles and 1 zero to the power stage:

## 600kHz 3A Step-Down Switching Regulator

Figure 3. Compensation network provides 2 poles and 1 zero.

The compensation network gives the following characteristics:

$$G_{COMP}(s) = \omega_1 \cdot \frac{1 + \frac{s}{\omega_Z}}{s \cdot (1 + \frac{s}{\omega_{P2}})} \cdot g_m \cdot \frac{R_2}{R_1 + R_2}$$

Where:

$$\omega_1 = \frac{1}{C_4 + C_5}$$

$$\omega_Z = \frac{1}{R_3 \cdot C_4}$$

$$\omega_{P2} = \frac{C_4 + C_5}{R_3 \cdot C_4 \cdot C_5}$$

The loop gain will be given by:

$$T(s) = G_{COMP}(s) \cdot G_{VD}(s) = 2.125 \cdot 10^{-3} \cdot \frac{R_{L}}{C_{4}} \cdot \frac{R_{2}}{R_{1} + R_{2}} \cdot \frac{1}{s} \cdot \frac{1 + \frac{s}{\omega_{Z}}}{(1 + \frac{s}{\omega_{P1}}) \cdot (1 + \frac{s}{\omega_{P2}})}$$

Where:

$$\omega_{\rm P1} = \frac{1}{\rm R_{\rm I} \cdot \rm C}$$

One integrator is added at origin to increase the DC gain.  $\omega_Z$  is used to cancel the power stage pole  $\omega_{P1}$  so that the loop gain has –20dB/dec rate when it reaches 0dB line.  $\omega_{P2}$  is placed at half switching frequency to reject high frequency switching noises. Figure 4 gives the asymptotic diagrams of the power stage with current loop closed and its loop gain.

Jan. 2010 – Preliminary

The design guidelines for the TJ4519 applications are as following:

- 1. Set the loop gain crossover corner frequency  $\omega_c$  for given switching corner frequency  $\omega_c = 2\pi f_c$

- 2. Place an integrator at the origin to increase DC and low frequency gains.

- 3. Select  $\omega_Z$  such that it is placed at  $\omega_{P1}$  to obtain a -20dB/dec rate to go across the 0dB line.

4. Place a high frequency compensator pole  $\omega_{P2}$  ( $\omega_{P2} = \pi fs$ ) to get the maximum attenuation of the switching ripple and high frequency noise with the adequate phase lag at  $\omega_{C}$ .

#### Layout Guidelines:

In order to achieve optimal electrical and thermal performance for high frequency converters, special attention must be paid to the PCB layouts. The goal of layout optimization is to identify the high di/dt loops and minimize them. The following guidelines should be used to ensure proper operation of the converters.

- 1. A ground plane is suggested to minimize switching noises and trace losses and maximize heat transferring.

- 2. Start the PCB layout by placing the power components first. Arrange the power circuit to achieve a clean power flow route. Put all power connections on one side of the PCB with wide copper filled areas if possible.

- 3. The VIN bypass capacitor should be placed next to the VIN and GND pins.

- 4. The trace connecting the feedback resistors to the output should be short, direct and far away from any noise sources such as switching node and switching components.

- 5. Minimize the loop including input capacitor, the TJ4519 and freewheeling diode D2. This loop passes high di/dt current. Make sure the trace width is wide enough to reduce copper losses in this loop. 6. Maximize the trace width of the loop connecting the inductor, freewheeling diode D2 and the output capacitor.

- 7. Connect the ground of the feedback divider and the compensation components directly to the GND pin of the TJ4519 by using a separate ground trace.

- 8. Connect Pin 4 to a large copper area to remove the IC heat and increase the power capability of the TJ4519. A few feed through holes are required to connect this large copper area to a ground plane to further improve the thermal environment of the TJ4519. The traces attached to other pins should be as wide as possible for the same purpose.

Jan. 2010 – Preliminary